Tentang VHDL

VHDL adalah bahasa untuk mendeskripsikan hardware elektronika digital; singkatan dari VHSIC Hardware Description Language. VHDL merupakan standar IEEE/ANSI dan Departemen Pertahanan US. Pertama kali dipublikasikan oleh IEEE pada tahun 1987, dengan label IEEE Std 1076-1987. Bahasa ini telah mengalami modifikasi dan revisi, dengan versi terbaru berlabel IEEE Std 1076-1993.

- VHDL singkatan dari VHSIC Hardware Description Language.

- VHDL dapat digunakan untuk menggambarkan desain elektronika digital pada beberapa tingkat abstraksi, dari skala tingkat algoritma hingga tingkat gate.

- VHDL pertama kali dikembangkan untuk Departemen Pertahanan US.

- Distandarisasi pertama kali oleh IEEE pada tahun 1987, dengan nama IEEE Std 1076-1987.

- Distandarisasi ulang pada tahun 1993, dengan nama IEEE Std 1076-1993.

- Sembilan nilai logika paket, disebut STD_LOGIC_1164, distandarisasi oleh IEEE untuk membantu di dalam interoperability model VHDL. Standar ini disebut IEEE Std 1164-1993.

- Beberapa kemampuan VHDL antara lain :

- Dapat digunakan sebagai exchange medium.

- Mendukung hirarki.

- Mendukung metodologi top-down dan bottom-up.

- Test bench dapat dituliskan menggunakan bahasa ini.

- Tipe data baru dapat disebutkan.

- Desain digital digambarkan dalam VHDL dengan menggunakan external view dengan satu atau beberapa internal view.

- External view menyatakan interface dari rancangan.

- Internal view menyatakan fungsi atau struktur dari rancangan. Suatu rancangan mungkin memiliki satu atau lebih internal view.

- Desain digital dapat juga digambarkan dalam VHDL dengan menggunakan beberapa external view yang berbeda.

- Tiap external view dan salah satu darinya berkaitan dengan internal view, yang secara bersama-sama merupakan representasi tertentu dari device, disebut dengan entity design.

- Library desain merupakan implementasi khusus tempat penyimpanan dalam host environment dimana deskripsi yang telah dikompilasi dapat disimpan.

- Satu atau lebih library desain yang ada harus memiliki nama logika, dimana pemetaannya pada lokasi fisik tertentu dinyatakan secara eksternal dalam host environment, jadi bukan menjadi bagian dari bahasa.

- Package yang ada: STANDARD dan TEXTIO. Keduanya terletak pada library desain STD.

- STD_LOGIC_1164 terletak pada library desain dengan nama IEEE. Tipe-tipe dasarnya adalah STD_ULOGIC, STD_LOGIC, STD ULOGIC VECTOR dan STD LOGIC VECTOR.

- Untuk simulasinya, pasangan entity-architecture top-level atau nama konfigurasi disebutkan.

- Tiga step simulasi: elaboration, initialization, simulation.

- Selama fase inisialisasi setiap proses dieksekusi satu kali dan semua sinyal diberi harga awal.

- Simulasi selanjutnya didasarkan pada waktu dari event selanjutnya.

- Blok bangunan paling dasar dalam suatu design.

- Deskripsi interface antara suatu entity disain dengan environment yang digunakan.

- Bukan definisi behavioral

- Penyambungan via port signal

– Tipe data

– Lebar signal

– signal direction (in, out, inout)

Architecture – Lebar signal

– signal direction (in, out, inout)

- Implementasi design.

- Selalu berhubungan dengan entity tertentu.

– Port entity sebagai sinyal

- Mengandung concurrent statement

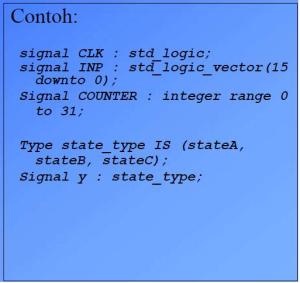

Tipe Data Obyek.

- STD_LOGIC dan

STD_LOGIC_VECTOR.

- STD_ULOGIC

- SIGNED dan UNSIGNED

- INTEGER

- REAL

- BOOLEAN

- ENUMERATION

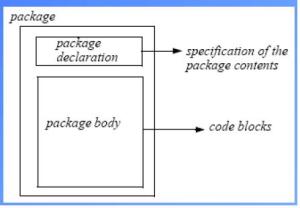

Libraries and Packages

- Libraries are logical units that are mapped to physical directories

- Packages are repositories for type definitions,

procedures, and functions

Standart Library Ada 4:

- LIBRARY IEEE ; ( Membaca Paket Standart Dari Library IEEE)

- USE IEEE.IEEE.STD_LOGIC_1164.ALL; (Memasukan Semua Bagian Dari IEEE STD_LOGIC Variable )

- USE IEEE.STD_LOGIC_ARITH_ALL; ( Memasukan Semua Operasi Aritmatika Untuk Standart Logic Variable)

- USE IEEE.STD_LOGIC_UNSIGNED.ALL; ( Memasukan Semua Fungsi Yang Belum Di Desain Untuk Operasi Arithmatic )

– Package declaration

library ieee;

use ieee.std_logic_1164.all;

package basic_func is

— AND2 declaration

component AND2

generic (DELAY: time :=5ns);

port (in1, in2: in std_logic; out1: out std_logic);

end component;

– OR2 declaration

component OR2

generic (DELAY: time :=5ns);

port (in1, in2: in std_logic; out1: out std_logic);

end component;

end package basic_func;

Sumber ; http://www.interfacebus.com/Design_VHDL_Pitfalls.html

http://www.faculty.petra.ac.id/herisw/rse.ppt

1 Komentar:

Do you have a spam problem on this website; I also am a blogger, and I was

curious about your situation; we have developed some

nice practices and we are looking to swap solutions with other folks, please

shoot me an e-mail if interested.

Here is my page :: a Extreme Fucking

Post a Comment

Silahkan tinggalkan pesan, Jangan pake SPAM ya!!! terima kasih !!